| | |

| Stránka: 1 z 1

| [ Príspevkov: 4 ] | |

| Autor | Správa |

|---|

Registrovaný: 17.02.14

Prihlásený: 31.03.24

Príspevky: 450

Témy: 198

Bydlisko: Poprad-okolie |

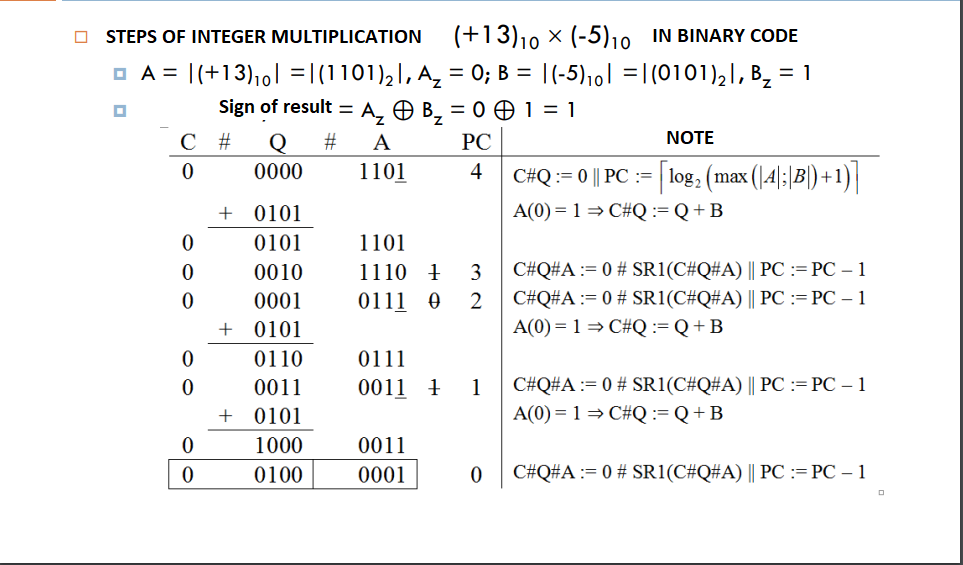

Ahoj, mojou úlohou je navrhnúť VHDL kód, ktorý má byť parametrizovateľný pre vstupný počet parametrov: Premenné: A[n-1: 0], B [n-1: 0], Q [n-1: 0], C [1] a PC sú registre. PC slúži ako počítadlo cyklov. Mám používať C#Q#A pre zreťazenie registrov. Algoritmus násobenia integerov: Kód: BEGIN

C#Q :=0 || PC:=n

WHILE(PC>0)

IF A(0) = 1 THEN

C#Q := Q+B

ENDIF

C#Q#A :=0 # SR1(C#Q#A)||

PC := PC - 1

END

END Ešte mám k tomu obrázok násobenia integerov v binárnom kóde. Neviem sa ani odraziť, ako mám formulovať ten kód, aby bol parametrizovateľný? Ako mám zapísať tie vstupné registre? Mám použiť štandardný in std_logic? Vďaka!

|

|

Registrovaný: 07.04.12

Prihlásený: 02.06.21

Príspevky: 907

Témy: 54 |  Napísal Napísal ado130 ado130: 16.12.2017 17:14 | |

|

Pod pojmom parametrizovateľný predpokladám majú na mysli, že šírka zbernice bude podľa nejakého parametra, tzn. pozri sa na generic - generic VHDL.

_________________

Notebook: Dell Inspiron 15-7537= i5-4200U|nVidia GT 750M 2GB|RAM 6GB|250GB Samsung 850 EVO|W8.1|Cooler Master NotePal U3

Pc: Asus Rog Strix B360-G | i7-8700 | MSI 1080 Gaming X | Crucial Ballistix 16GB 2666MHz Dual Ranked | Samsung 970 Evo | Crucial MX500 | WD Red | Fera 3 | Arctic F12 Silent | Seasonic Focus Plus 650W Gold | Fractal Design Mini C TG

Disk: Western Digital Elements 1TB USB 2.0; Seagate Expansion 2TB USB 3.0

Príslušenstvo: A4tech Bloody V3 V-Track Core 3 + A4tech Bloody B-070; A4tech Bloody B120; A4tech Bloody G501; ATH-M40x; MSI Clutch M40

Monitor: Dell U2515H

Mobil: Xiaomi Redmi Note 3 Special Edition |

|

Registrovaný: 17.02.14

Prihlásený: 31.03.24

Príspevky: 450

Témy: 198

Bydlisko: Poprad-okolie |

Mám problém s test benchom: Kód: library IEEE;

use IEEE.Std_logic_1164.all;

use IEEE.Numeric_Std.all;

entity nasobenie_tb is

generic

(

DATA_WIDTH : natural := 4

);

end;

architecture bench of nasobenie_tb is

component nasobenie

generic

(

DATA_WIDTH : natural := 2

);

port

(

a : in signed ((DATA_WIDTH-1) downto 0);

b : in signed ((DATA_WIDTH-1) downto 0);

q : out signed ((2*DATA_WIDTH-1) downto 0)

);

end component;

signal a: signed ((DATA_WIDTH-1) downto 0);

signal b: signed ((DATA_WIDTH-1) downto 0);

signal q: signed ((2*DATA_WIDTH-1) downto 0) ;

begin

-- Vlozenie hodnot pre parameter generic !!

uut: nasobenie generic map ( DATA_WIDTH => DATA_WIDTH )

port map ( a => a,

b => b,

q => q );

stimulus: process

begin

a <= "00";

b <= "00";

wait for 10 ns;

a <= "00";

b <= "01";

wait for 10 ns;

a <= "00";

b <= "10";

wait for 10 ns;

a <= "00";

b <= "11";

wait for 10 ns;

a <= "01";

b <= "00";

wait for 10 ns;

a <= "01";

b <= "01";

wait for 10 ns;

a <= "01";

b <= "10";

wait for 10 ns;

a <= "01";

b <= "11";

wait for 10 ns;

a <= "10";

b <= "00";

wait for 10 ns;

a <= "10";

b <= "01";

wait for 10 ns;

a <= "10";

b <= "10";

wait for 10 ns;

a <= "10";

b <= "11";

wait for 10 ns;

a <= "11";

b <= "00";

wait for 10 ns;

a <= "11";

b <= "01";

wait for 10 ns;

a <= "11";

b <= "10";

wait for 10 ns;

a <= "11";

b <= "11";

wait for 10 ns;

end process; --koniec opisu procesov

end bench; --koniec opisu architektury tb

Problém nastáva pri kompilácii Testbenchu, kedy nesedí generic downto, ale nechápem prečo.. V tb chcem mať 2-bitový integer a výsledok je 4-bitový integer. Kde je problém? Mám to dosť podobne zapísané aj v normálnom VHD kóde, kde mám 8 pre výsledok a 4 pre vstupné int a Waveform zbehne v poriadku, vykreslí sa. Chybová hláška: Kód: # ** Fatal: (vsim-3420) Array lengths do not match. Left is 4 (3 downto 0). Right is 2 (3 downto 2).

# Time: 0 ps Iteration: 0 Process: /nasobenie_tb/stimulus File: D:/altera/13.0sp1/nasobenie/nasobenie_tb.vhd

# Fatal error in Process stimulus at D:/altera/13.0sp1/nasobenie/nasobenie_tb.vhd line 41

#

|

|

Registrovaný: 07.04.12

Prihlásený: 02.06.21

Príspevky: 907

Témy: 54 |  Napísal Napísal ado130 ado130: 06.01.2018 21:40 | |

|

Raz je tam DATA_WIDTH ako 4 bitovy a raz ako 2, nemôže byť chyba v tom?

// Spojený príspevok Ned 07.01.18 9:25

Myslím, že to tak bude. Pretože v komponente si nastavil šírku 2 bity, ale pre signály a b q 4 bity. Následne si ich prepojil - už tu je divné že to nehučí chybu, ale následne sa snažíš priradiť 2bitove číslo do 4 bitoveho signálu.

_________________

Notebook: Dell Inspiron 15-7537= i5-4200U|nVidia GT 750M 2GB|RAM 6GB|250GB Samsung 850 EVO|W8.1|Cooler Master NotePal U3

Pc: Asus Rog Strix B360-G | i7-8700 | MSI 1080 Gaming X | Crucial Ballistix 16GB 2666MHz Dual Ranked | Samsung 970 Evo | Crucial MX500 | WD Red | Fera 3 | Arctic F12 Silent | Seasonic Focus Plus 650W Gold | Fractal Design Mini C TG

Disk: Western Digital Elements 1TB USB 2.0; Seagate Expansion 2TB USB 3.0

Príslušenstvo: A4tech Bloody V3 V-Track Core 3 + A4tech Bloody B-070; A4tech Bloody B120; A4tech Bloody G501; ATH-M40x; MSI Clutch M40

Monitor: Dell U2515H

Mobil: Xiaomi Redmi Note 3 Special Edition |

|

| Stránka: 1 z 1

| [ Príspevkov: 4 ] | |

Podobné témy | | Témy | Odpovede | Zobrazenia | Posledný príspevok |

|---|

| VHDL kód pre Rnon Snon preklápací obvod založený na NAND v Elektronika | 16 | 964 | 24.11.2017 0:06 martinius96  |  | IDEA pre Ochranny kod v PHP, ASP | 8 | 619 | 28.03.2008 21:39 proxy  |  | iny kod pre IE v HTML, XHTML, XML, CSS | 3 | 609 | 27.09.2009 16:37 Ďuri  |  | Hra pre dvoch v Počítačové hry | 12 | 2213 | 30.12.2013 8:33 kamikadzeee  |  | FREE program pre HTML kod v Ostatné | 7 | 1646 | 30.11.2008 11:59 Blackshadow  |  | Nasobenie v JavaScript, VBScript, Ajax | 9 | 1023 | 24.02.2008 19:03 eiger33  |  | Hry na PS5 pre dvoch v Herné konzoly | 1 | 411 | 24.10.2023 8:11 fallenblue  |  | P: Kód na Unravel pre XBOX ONE v Predám | 0 | 314 | 24.08.2016 10:04 nicolai  |  | I/K registracny kod pre koss sluchadla v Kúpim | 2 | 367 | 11.03.2013 21:50 citronik  |  | xbox hry pre dvoch hracov sucasne v Herné konzoly | 3 | 1265 | 22.04.2012 10:58 EXIREXT  |  | I/P: Kod na PUBG pre xbox one v Predám | 0 | 264 | 10.07.2018 13:16 Renegate  |  | nasobenie pola Pascal v Assembler, C, C++, Pascal, Java | 8 | 472 | 15.06.2013 22:47 dany2281995  |  | C++ nasobenie vacsich cisel v Assembler, C, C++, Pascal, Java | 5 | 744 | 30.12.2009 12:32 josi  |  | Kroneckerovske nasobenie v C j. v Assembler, C, C++, Pascal, Java | 8 | 696 | 28.11.2008 16:14 suchy  |  | Násobenie a delenie v assembleri v Assembler, C, C++, Pascal, Java | 4 | 2769 | 01.11.2007 20:01 martin90  |  | PhysX pre všetky nové GeForce karty do dvoch týždňov v Novinky | 10 | 783 | 25.07.2008 22:32 Spirit  |

| Nemôžete zakladať nové témy v tomto fóre

Nemôžete odpovedať na témy v tomto fóre

Nemôžete upravovať svoje príspevky v tomto fóre

Nemôžete mazať svoje príspevky v tomto fóre

|

|